本文要点

PCB 差分对的基础知识。

差分对布线指南,实现更好的布线设计。

高效利用 PCB 设计工具。

“众人拾柴火焰高” ——资源整合通常会带来更好的结果。毕竟 “三个臭皮匠,顶个诸葛亮”,在电子领域也是如此:较之单一的走线,差分对布线更受青睐。

不过,差分对布线可能没那么容易,因为它们必须遵循特定的规则,这样才能确保信号的性能。这些规则决定了一些细节,如差分对的走线宽度和间距,以及许多其他方面,如导线如何在电路板上一起布线。如果使用了大量的差分对,即使设计师已经为每个信号布设了两条单独的走线,也会对电路板其他部分的布线产生很大的影响。本文将详细介绍差分对的布线和一些需要注意的潜在问题。

1. PCB 差分对的基础知识

在开始了解差分对布线的潜在困难和解决方案之前,先回顾一下基础知识。有过 PCB layout 经验的人一定熟悉单端信号。单端信号是指在一条走线上传输信号,然后使用一个共同的参考平面作为信号的返回路径。当我们在电路板上布线时,接地平面是信号的返回路径,这就是单端信号。大多数 PCB 网络都是这样布线的。

然而,这种布线方式有一个问题:随着传输线速度提高,单端信号可能会受到一些问题的影响,包括串扰噪音和电磁干扰 (EMI)。此时,差分信号就派上了用场。

差分信号使用两个互补的信号来传输一个数据信号,但第二个信号与第一个信号的相位相反。信号接收器使用反相和同相信号之间的差异来破译信息。使用差分对布线传输信号有一些重要的好处,首先是能减少噪音和 EMI:

传入的干扰将被均等地添加到反相和同相的信号中。由于接收器是对两个信号之间的差异作出反应,无论是否受到影响,影响都是最小的。与影响单端信号的干扰相比,这样的性能要好得多。

差分对的电磁场大小相等,但极性相反,因此来自两条走线的干扰通常可以相互抵消。

印刷电路板上的差分对布线

与单端信号相比,差分对还有一个优势,那就是它们可以在较低的电压下工作。单条走线必须在较高的电压下工作,以确保其信噪比 (SNR) 足以抵御任何传入的噪声。差分对对噪声的抗干扰能力更强,因此需要的电压更低,这提供了一些额外的好处:

所需的电压更低意味着功耗也更低。

信号的电压转换将更小,有助于确保电路板的电源完整性。

在较低的信号电压下可以使用较高的工作频率。

电压越低,辐射的 EMI 就越少。

如上所述,在电路板上使用差分信号有诸多好处,但也要付出一些代价。

2. PCB layout 中与差分对相关的问题

如上文所述,使用差分对布线有诸多好处,但也有一些缺点。第一个也是最明显的问题是,必须为每个信号布设两条走线。这不仅使电路板上的布线量增加了一倍,而且由于差分对有额外的规则,还会占用更多的空间。我们来看看设计师在进行差分对布线时不得不面对的一些难题。

差分对中两条走线的长度必须相等

差分对的一大优势是,通过两个极性相反的均等信号来代表信号,可以消除噪声和 EMI。但如果线路的长度不相等,这种平衡就会遭到破坏,并可能反过来产生共模噪声和严重的 EMI 问题。如果线路的长度不一致,信号的上升和下降时间越长,问题就会越严重。

差分对走线的宽度和间距必须始终保持一致

走线靠得越近,差分对之间的耦合性就越好。然而,当走线的间距发生变化时,差分阻抗也会发生变化,从而导致阻抗不匹配以及额外的潜在噪声和 EMI。

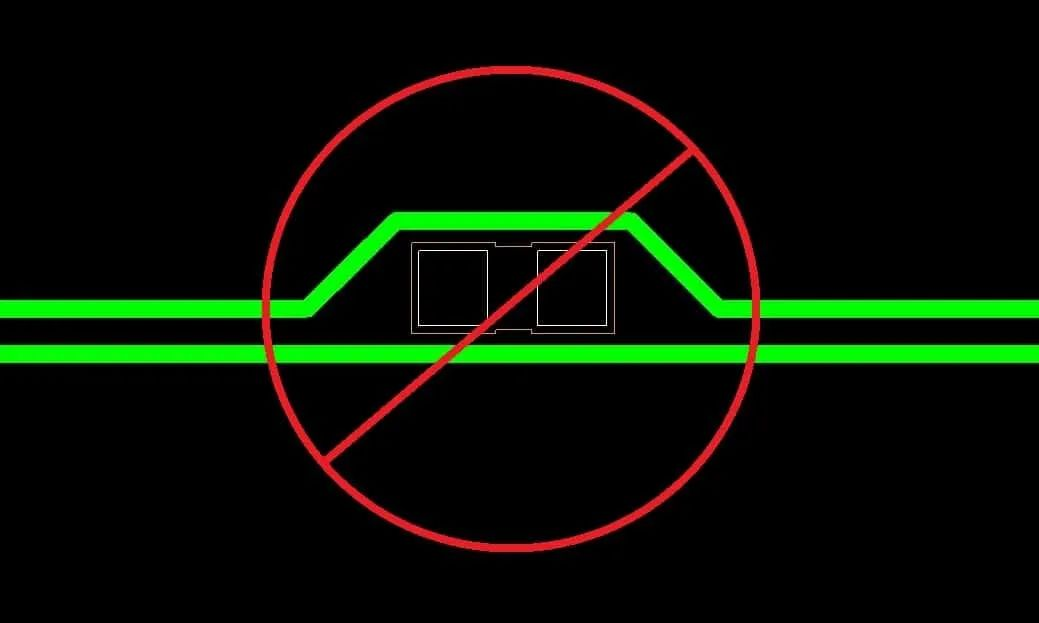

为了避免这种情况,差分对必须一起布线,并且宽度要相同,当在电路板上的障碍物(如过孔或较小的器件)周围进行布线时,这可能是个难题。

示例:不在障碍物周围进行差分对布线

为了让差分对布线发挥最佳性能,要遵循一些基本规则,接下来将一一讨论。

3. 差分对布线指南

为了在电路板上获得最佳的信号性能和完整性,以下是 PCB 设计师需要注意的一些差分对布线规则:

差分对需要一起布线

对于布线团队来说,差分对的两条走线需要清楚地标记为差分对,以便在信号的整个长度上一起布线。

如果可能的话,尽量避免使用过孔。如果必须要使用,应该对称摆放一对过孔。尽量使过孔靠得很近,它们相对于布线焊盘的位置应该是均等的。

最好使用内层布线,以尽量减少串扰,但这意味着使用过孔过渡到各层。

确保差分对与其他走线彼此分离。通常,间隔距离应为正常走线宽度间距的三倍。

如果可能的话,考虑在相邻的信号层上进行侧面差分对布线。这将带来更高的布线密度和更好的串扰控制。

两条走线之间的布线保持对称

成功的差分对布线应该使两条线路之间形成镜像。要做到这一点,在布线时要考虑:

规划布线方式,避免障碍物,如过孔或无源器件,以保持差分对的对称性(如上图所示)。

规划焊盘入口和出口的布线,使走线之间尽可能形成镜像。

在走线的整个长度上使用相同的走线宽度。

差分对走线之间的间距保持一致。

差分对走线的长度保持一致

如前所述,差分对走线的长度必须是相同的。为此,可以在较短的那条线路上添加蛇形走线,使两者长度相等。虽然这将稍微改变线路的对称性,但长度相等更加重要。如果长度不均等是由于焊盘位置不对称,可试着在线路的这个区域添加蛇形走线。

虽然在进行差分对布线时需要关注很多问题,但 PCB 设计 CAD 工具通常有很多功能,可以帮助我们配置差分对布线的方式。

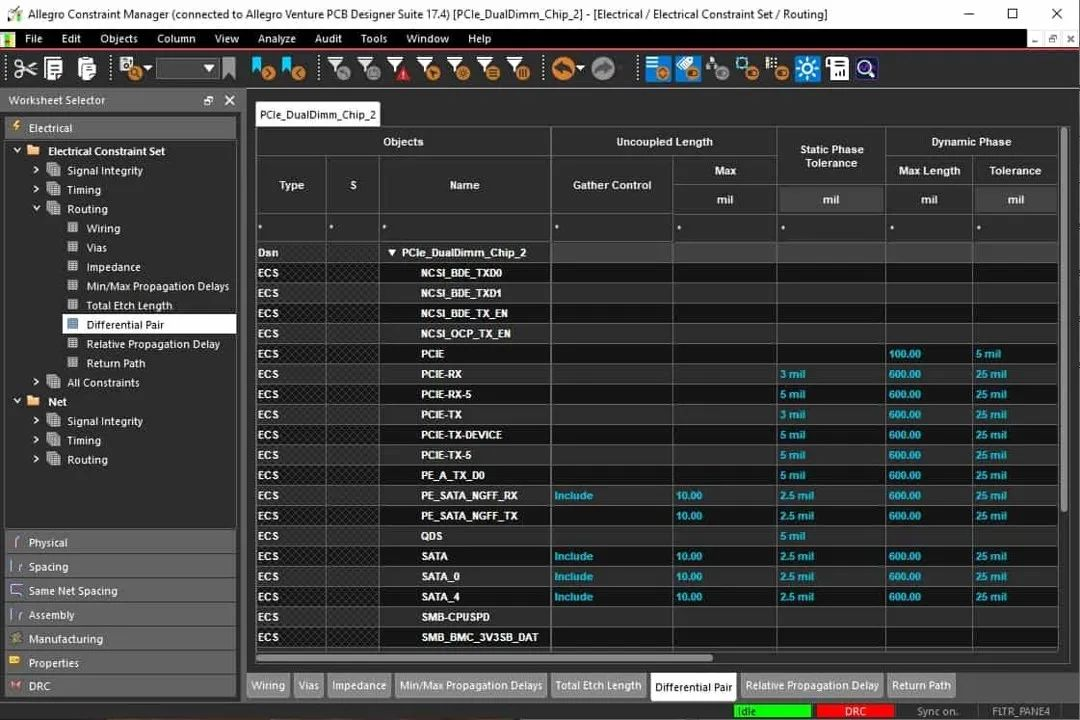

Cadence Allegro PCB Designer 约束管理器中的差分对布线规则

使用PCB CAD 工具进行差分对布线

曾几何时,PCB layout 设计师只能手动进行差分对布线。他们需要花费大量精力来确保线路保持对称,而在布线之后再修改走线堪称一场噩梦。现在, Cadence Allegro PCB Designer 这样的工具提供了自动的差分对布线功能,在布线时可以轻松确保差分对之间保持适当的宽度和间距。此外,还可以添加规则和约束,以管理差分对的各个方面。

在上图中可以看到,Cadence 的 PCB layout 工具中使用 Constraint Manager 来管理包括差分对在内的不同设计规则。其中包括走线的宽度和间距,允许走线蜿蜒的长度,以及布线图,包括焊盘的入口和出口。借助这一工具,我们可以为差分对输入所有相关的规则,确保它们符合具体的电路需求。

文章来源:Cadence楷登PCB及封装资源中心