引言

PCB布线犹如“太祖长拳",人人会使,但掌握电路原理精髓方能如同金大侠笔下之萧峰聚贤庄大战各路英豪使用太祖长拳之描写“这一招姿势既潇洒大方已极,劲力更是刚中有柔,柔中有刚,武林高手毕生所盼望达到的拳术完美之境,便在这一招中表露无遗。”萧峰运用太祖长拳对战三高僧能够完胜,完全是仗着他的深厚内功,了解电路工作原理是PCB Layout工程师所需要具备的内功。

前言

C200 和 C210 电源IP都是同步降压转换器,与所有开关电源转换器一样,在设计 PCB 时必须小心,以避免后续产生难以解决,不可预测的问题。

地平面选择

PCB 中第二层最好用作接地层,这将最大可能地减少顶层过孔接地的长度、减少线路杂散感抗,同时接地层还将充当顶层同步降压电源的开关节点和第 3 层中敏感信号之间的法拉第屏蔽层。同样,对于六层或者更多层数PCB,第 2 层到最后一层也最好用作接地层。通用规则,所有接地的元件引脚都应在其附近或引脚上有接地过孔,尤其是旁路电容器。最后,应在整个电路板空白区域添加尽可能多的接地过孔以将接地层连接在一起,这些接地过孔在功率部分的区域尤其重要,而在非功率部分的电路板空白区域中则不太重要。

Lx 走线阻抗损耗

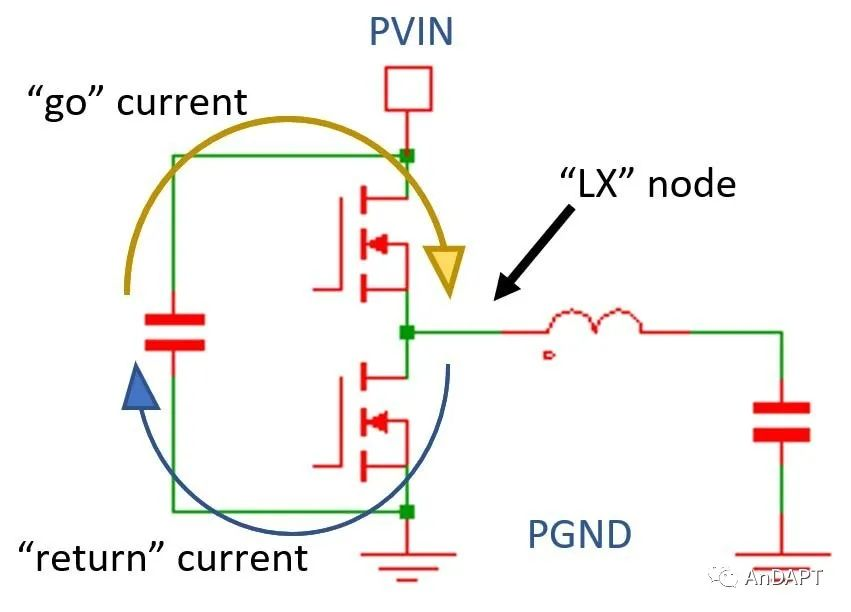

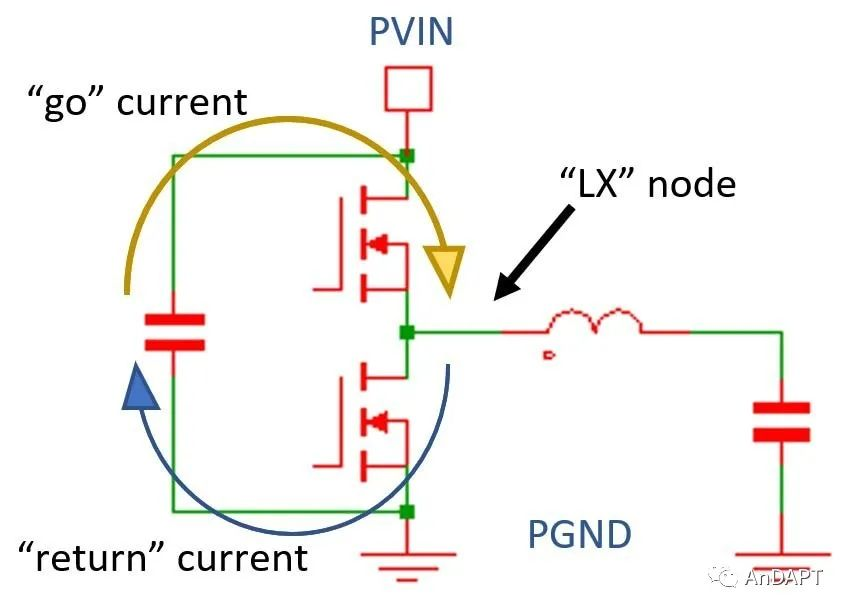

如图一所示,上图中的黑色箭头指向的是Lx节点,它是半桥输出的开关节点,连接到电感。因为它承载大电流,所以走线需要很宽,以尽量减少降低系统效率的电阻损耗。可以参考https://www.edn.com/resistance-of-a-copper-trace-rule-of-thumb-14/(EDN 杂志:“PCB走线电阻:经验法则 #14”)文章,此文章介绍了一条用于快速计算由电阻损耗引起的满载效率损失百分比(%LOSS)的经验法则,包含如何使用“每平方欧姆”和“平方数”快速估算PCB走线电阻 RTRACE 的方法。

%LOSS = Vloss / VO , VO是输出电压

Vloss = IO * RTRACE ,IO是满载电流, RTRACE是(平方数)*(欧姆/平方)

图一: 同步降压转换器主开关回路和高边 dv/dt 节点

dv/dt 噪声耦合

Lx节点是半桥输出的开关节点,在PWM开关边缘具有快速电压变化率dv/dt,由于Lx需要很宽的走线满足额定峰值电流的要求,所以它具有很强的能力将 dv/dt 噪声耦合到同层或者其他层的敏感信号的PCB走线,敏感信号是指那些具有高阻抗和低电压的信号。具有快速电压变化率dv/dt的节点和敏感信号之间的杂散电容会导致来自前者的噪声耦合到后者的信号中。

如果没有接地层或者电源层充电法拉第屏蔽层,务必保证任何敏感信号的 PCB 走线不要在 LX 走线正下方的层中, 否则,由于它们之间存在杂散电容,敏感信号会被注入 dv/dt 噪声。

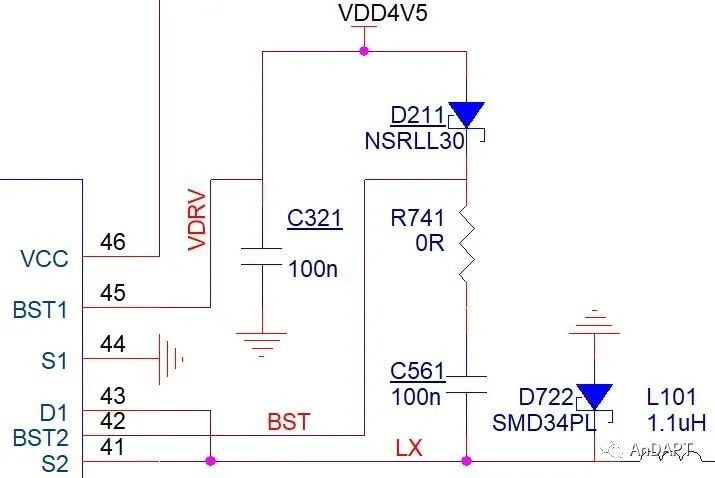

此外,如图二所示,高边 BST引脚(栅极驱动自举, 图 中的引脚 42/BST2)和连接到它的器件(C561、R741 和 D211 的阴极)具有与 LX 节点相同的 dv/dt,确保这些器件及其走线同样不会将 dv/dt 噪声耦合到敏感信号的的走线中。

图二:自举电路 C561、可选 R741 和 D211 、可选的续流二极管 D722

主开关回路

再次引用图一,电流在回路中流动,具有高 di/dt 的同步降压转换器中的主开关环路如图所示,它由半桥主 MOSFET 以及与最近的 PVIN 旁路电容器的连接构成。黄色曲线箭头代表“输出”电流,蓝色曲线箭头代表“返回”电流,它们一起形成一个电流循环,其包围的面积需要最小化。

我们要注意的是,在绝大部分时间,电流实际上都不会在此环路中流动,除非在很短的时间内,PWM高边开启边沿对低边 MOSFET Coss 充电并驱动其体二极管反向恢复电流。相反,在此环路中的所有电流分支都具有较大的 di/dt,它们在开关转换期间快速电流变化,并且这些分支的 di/dt( 箭头方向,不是绝对电流方向)形成一个完整的环路,如果这个环路面积很大,不仅会辐射出di/dt噪声,而且这个大面积环路形成的杂散电感会和旁路电容形成谐振,这种谐振会在 如下图三所示的AmP芯片半桥的PVIN 和 PGND 端子引起振铃,严重的振铃会导致难以预测的莫名其妙的问题。

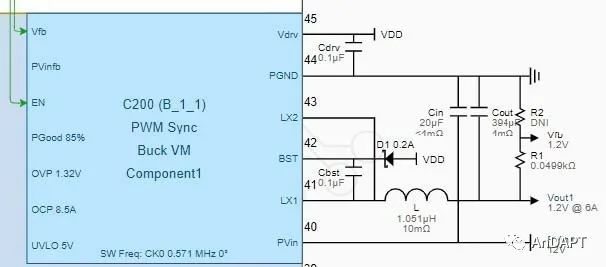

图三:WebAmP C200原理图

PCB 布局中最小化此环路面积的方法之一是相邻层中的电流输出和返回路径是叠加状态,顶层上的电流输出在第 2 层的接地层正下方具有相应的未被分割的返回电流路径。实现这种布局的最好方法是PVIN同层引脚处放置一个小电容,并且PCB下一层就是接地层,其他较大容量的旁路电容可以布置的稍微远一些,比如放置在电路板的反面,通过较多过孔连接。所有 PVIN上的 旁路电容器都需用足够宽的走线将旁路电容的PVIN连接到 AmP 器件的 PVIN 引脚,如果有电源层,PVIN 附近就应该有足够多的过孔。

低端 MOSFET 的源极引脚

低端 MOSFET 的源极引脚(标记为“PGND”)芯片内部没有接地连接,此引脚需与接地层连接,此连接杂散电感越小越好。建议使用至少两个过孔直接打在焊盘上, 通常使用钻孔直径为 6 mil 或 0.15 mm 的过孔。需要注意的是,PCB 制造商应该填充并平整焊盘中的过孔,以确保SMT焊接可靠性。芯片中间的EPAD接地应该和源极在同层相连。

过孔阻抗估算

“每平方欧姆”方法也可用于估计过孔阻抗,其中

平方数= 过孔长度 / (π * 过孔直径)

如果过孔是顶层连接到第二层,对于六层板来说,过孔的典型值是6Mil, 因此对于6Mil直径的过孔平方数是0.5平方。除非特殊工艺,一般过孔内的镀层通常只有 ½ 盎司厚 (18 µm),相比较而言,如果顶层是1盎司厚度,那么这个过孔的阻抗和顶层的1平方相同,如果顶层是2盎司厚度,这个过孔的阻抗就是2平方。如果接地层是6层板中的第5层,过孔的阻抗将增加4到5倍, 显而易见,将第 2 层用作大电流连接的接地层明显具有优势。

PCB 制造商可以用导热和导电材料填充过孔, 这改善了电和热传导,这是 AmP 器件EPAD的优势。 可以咨询PCB 制造商了解其电导率常数,以便计算其热阻和阻抗。另外,对于热要求苛刻的应用,除EPAD之外,MOSFET 源极和漏极引脚还提供了额外的器件散热路径, 连接到这些引脚的通孔和铜线将有助于带走热量。

布线案例

案例一,Lx节点同层连接电感

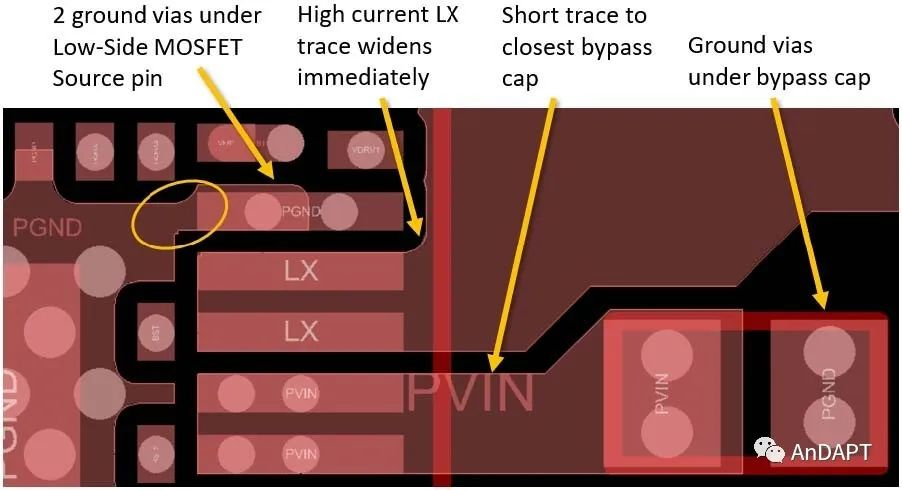

图四示例了我们以上讨论的 4 个要点,AmP 器件EPAD连接到低侧边MOSFET 源极引脚。

图 4:LX 走线使用同层的示例布局。电感位于右上角(未显示), 圆圈显示接地覆铜连接到低侧 MOSFET 源极引脚。

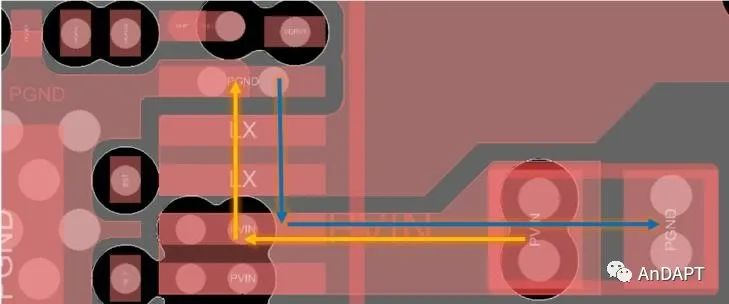

图五显示了电流环路路径,地平面显示为白色阴影。“输出”电流用黄色箭头表示,“返回”电流用蓝色箭头表示。需要注意的是,高频电流是以物理上最小化的环路面积流动。在此示例中,输出电流下方的接地层是完整的,如蓝色箭头所示,如果接地层位于下一层,则可以使环路面积物理上尽可能小。蓝色箭头所在的接地平面中的任何中断都会增加环路面积,我们应该避免。

图 5:与图 4 相同的布局,显示图 1 中描述的接地层(白色阴影)和高频电流环路

案例二:Lx双层布线

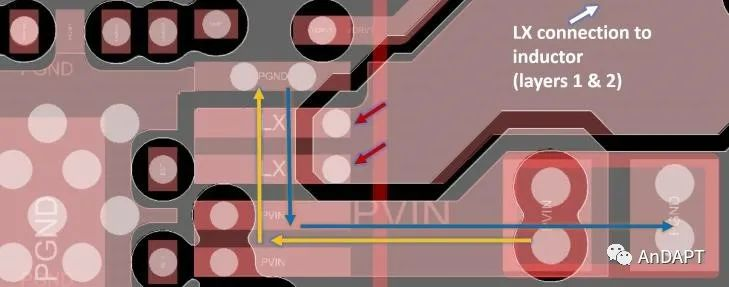

有时由于布局限制,Lx在顶层无法做到满足峰值电流所需的走线宽度,但仍然需要尽可能地提高电源效率。在这种情况下,第 2 层(接地层)用于并联Lx走线来分流电流。 图六为一个类似布线案例,但是我们还是要尽可能不使用接地层以减少阻抗损耗。为了实现合适的电流分流,第 2 层的铜岛应该尽可能在靠近电感的引脚处放置尽可能多的过孔。

必须尽可能保持电流“输出”路径(黄色箭头)和“返回”路径(蓝色箭头)的连续性,Lx引脚上连接到第二层的过孔位置(红色小箭头)尽可能靠近外部(右)放置,以便垂直的蓝色箭头不间断。

图 6:使用第 2 层与顶层并联的布局,用于 Lx 连接到电感(未显示,右上方)

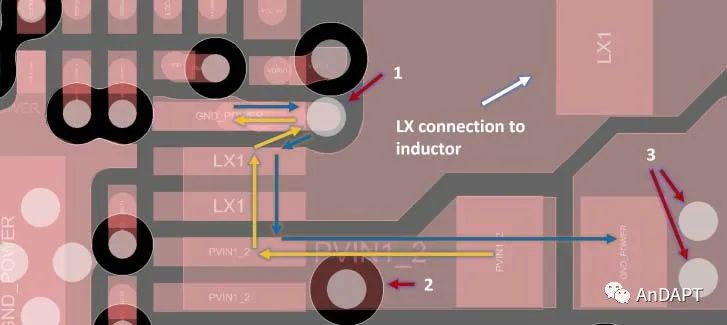

案例三:不在焊盘上打过孔的Lx布线

如图七所示,C200 源极的接地过孔应非常靠近引脚(红色箭头“1”),最近的旁路电容器的接地过孔也需要非常靠近其接地引脚(红色箭头“3”)。红色箭头“2”的过孔将 PVIN 节点连接到内层中的走线(未显示),将它放置在下方,因此不会中断电容的输出电流(黄色长水平箭头)。如果焊盘中没有过孔,Lx 与电感的连接会有些窄,这或许会对效率有一些影响。

图 7:与图 5 相同的布局,但焊盘上不打过孔

其他需要低感抗布线的外围器件

还有一些需要注意的外围器件布线, 这些外围器件需要和 AmP 器件引脚之间形成一个小的环路区域。也就是说,它们需要相对靠近 AmP 器件,并且走线较短,具有接地端子的器件应就近接地。 理论上,没有引脚接地的器件也有各自独立的输出和返回路径。这些器件如下,

• 高边驱动自举肖特基 (D211)

• 栅极驱动旁路电容器

高边:连接到 BST2/3/6/7 引脚(图 3 中的 BST 引脚)到 Lx

低边:连接到 BST1/4/5/8 引脚(图 3 中的 Vdrv 引脚)到接地层

• 可选的低边 FET 反向并联肖特基(图 2 中的 D722 ), 此肖特基可以将效率提高2%,但高阻抗的走线会降低效率。 此肖特基二极管是可选项,取决于PCB面积。

输出电容和反馈感应

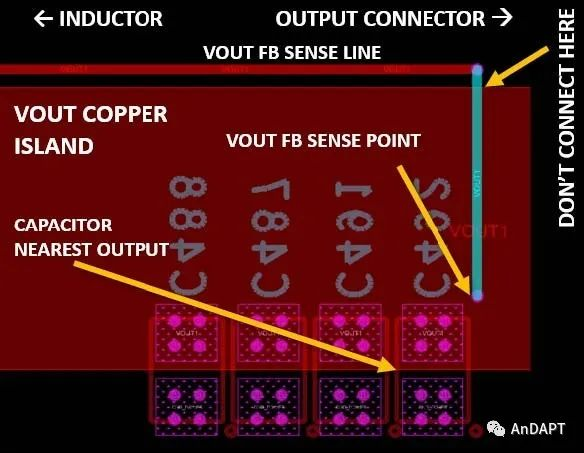

输出电容器必须与负载具有低感抗连接,高感抗的走线会降低输出电源轨的瞬态响应。从输出 VOUT 到 C200 反馈输入(图八中 R1 的底部)的电压反馈检测连接点必须位于最靠近负载的输出电容器处。将其连接到靠近电感会降低负载瞬态性能。在原理图和 PCB 布局中,电压反馈走线与 VOUT 是同一个网络,但布线时必须小心,确保只有一个连接点,通常最后一个输出电容器为采样连接点。图 八 显示了使用单独的层(蓝色迹线),此单点连接位于靠近负载的输出电容器附近的过孔处,不要简单地将其连接到随机点的 VOUT 铜岛。

图 8:多个输出电容器的反馈采样点,蓝色走线连接在另一层并连接到靠近最后一个电容的过孔

摘要/布线检查清单

1) 第 2 层是接地层吗?

2) C210/C200 的 Source/PGND 引脚是否有至少2 个过孔打在焊盘上以连接到接地层,或者是在引脚旁边有过孔将其连接到接地层?

3) 最近的 PVIN 旁路电容是否以非常短的铜线连接到 C200/C210 的 PVIN 引脚?

4) 最近的 PVIN 旁路电容的接地焊盘是否在下方或附近有通向接地层的过孔?

5) 从源极/PGND 引脚到旁路电容器接地端子的返回路径是否在接地层中具有不间断的路径,如图 5 中的“环路电流”?

6) Lx 与电感的连接是否足够宽以减少电阻损耗?

7) 如果使用与电感的 Lx 连接并联的第 2 层铜岛,如图 6 所示,在环路电流下的返回电流是否在接地层中有不间断的路径?

8) 敏感走线与 Lx 或 BST 节点之间是否存在有问题的杂散电容?

9) 以下布线对 AmP 器件引脚的杂散电感是否足够低?

a.高边驱动自举肖特基二极管

b.栅极驱动旁路电容

i. 高边 BST 引脚

ii.低边 BST 引脚

c.可选的低侧 FET 反向并联肖特基二极管

10) 从输出电容到负载的连接是否具有低感抗

11) 反馈检测点是否在最后一个输出电容?

关于AnDAPT(安普芯源微电子)

AnDAPT是一家总部位于爱尔兰都柏林的Fabless半导体公司,其目标是为客户提供完全可编程的电源管理芯片解决方案,投资者包括Intel Capital,Cisco,Altantic Bridge, Enterprise Ireland,WestSummit Capital, Vanguard等。

本文转载自:AnDAPT微信公众号